Sourcing Guide Contents

Industrial Clusters: Where to Source China Fabless Semiconductor Companies

SourcifyChina B2B Sourcing Report 2026

Deep-Dive Market Analysis: Sourcing Fabless Semiconductor Companies in China

Prepared for Global Procurement Managers

Executive Summary

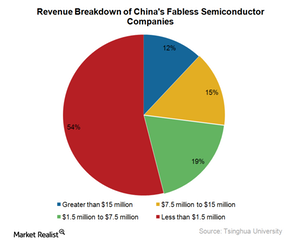

China’s fabless semiconductor sector has undergone rapid transformation over the past decade, driven by national strategic investment, rising domestic demand, and global supply chain diversification. As of 2026, China accounts for over 25% of global fabless semiconductor design companies, with concentrated industrial clusters in key coastal and inland provinces. This report provides a strategic overview of China’s fabless semiconductor landscape, identifying core manufacturing and design hubs, analyzing regional competitiveness, and offering actionable insights for global procurement managers.

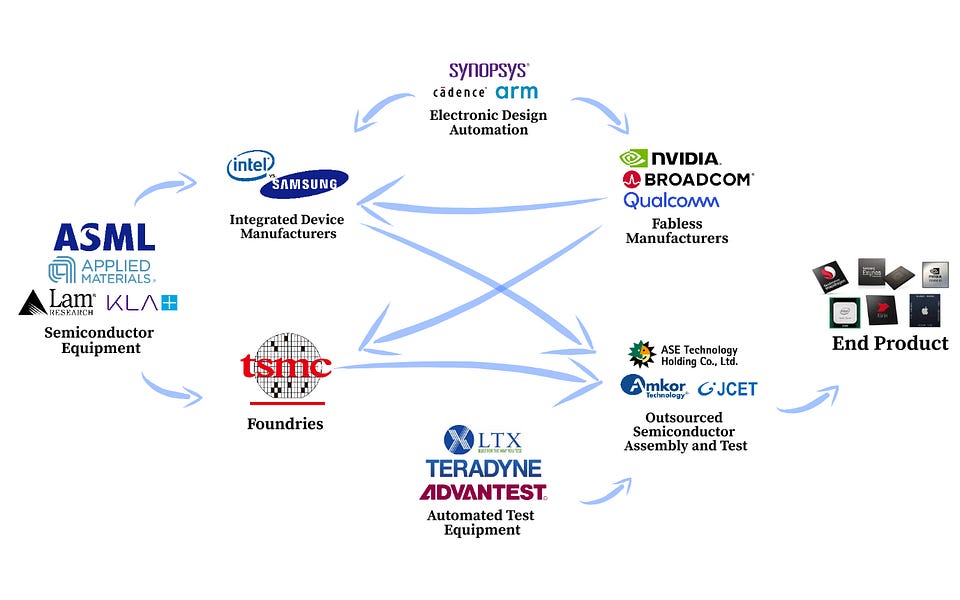

Fabless semiconductor companies in China specialize in integrated circuit (IC) design and outsource fabrication (to foundries such as SMIC, Hua Hong, or TSMC). These firms are critical partners for electronics OEMs in consumer electronics, automotive, industrial automation, and AI hardware. While China lacks domestic leadership in cutting-edge process nodes (sub-7nm), it dominates in mature-node applications (28nm and above), power management ICs (PMICs), display drivers, and IoT microcontrollers.

This report focuses on the geographic clustering of fabless companies, evaluates regional strengths in price competitiveness, quality assurance, and lead time, and offers procurement strategies aligned with 2026 supply chain realities.

Key Industrial Clusters for Fabless Semiconductor Companies in China

China’s fabless semiconductor ecosystem is regionally concentrated, with five primary clusters emerging as innovation and production hubs:

| Region | Core Cities | Key Strengths | Notable Companies / Incubators |

|---|---|---|---|

| Yangtze River Delta | Shanghai, Suzhou, Wuxi, Hangzhou | R&D leadership, access to capital, proximity to foundries | VeriSilicon, SMIC (design services), SiEn, Will Semiconductor |

| Pearl River Delta (Guangdong) | Shenzhen, Guangzhou, Dongguan | Electronics supply chain integration, fast prototyping, strong SME ecosystem | GigaDevice, Feitong Micro, Belling Inc., Ingenic Semiconductor |

| Beijing-Tianjin-Hebei | Beijing, Tianjin | Academic R&D, government support, AI and communication ICs | Will Semiconductor (HQ), UNISOC (partially fabless), Horizon Robotics |

| Chengdu-Chongqing | Chengdu, Chongqing | Labor cost advantage, inland policy incentives, automotive electronics | Silan Microelectronics, Chipown, Maxscend Microelectronics |

| East China (Zhejiang) | Hangzhou, Ningbo | IoT and consumer IC specialization, private investment | H&T (Hangzhou Zhongce), Sanan IC, Feitong Micro (subsidiary) |

Regional Comparison: Fabless Semiconductor Sourcing Metrics (2026)

The table below compares key sourcing regions in China for fabless semiconductor design partners based on price competitiveness, quality consistency, and lead time performance—critical KPIs for global procurement operations.

| Region | Price Competitiveness (1–5) | Quality Consistency (1–5) | Lead Time (Design to Sample) | Key Advantages | Procurement Risks |

|---|---|---|---|---|---|

| Guangdong (Shenzhen/Guangzhou) | 4.5 | 3.8 | 6–8 weeks | Rapid NPI, agile SMEs, strong EMS integration | Variable quality control, IP protection concerns |

| Zhejiang (Hangzhou/Ningbo) | 4.0 | 4.2 | 8–10 weeks | High IoT focus, stable mid-tier suppliers, strong local governance | Limited scale for high-volume production |

| Shanghai/Suzhou (Yangtze Delta) | 3.8 | 4.8 | 10–12 weeks | Premium quality, mature processes, strong IP frameworks | Higher costs, longer lead times |

| Beijing | 3.5 | 4.7 | 12–14 weeks | Cutting-edge R&D, AI/5G expertise, government-backed innovation | High cost, export controls on advanced tech |

| Chengdu/Chongqing | 4.7 | 3.6 | 8–10 weeks | Low labor costs, policy incentives, automotive focus | Infrastructure lag, talent retention challenges |

Scoring Note:

– Price: 5 = Most competitive pricing, 1 = Premium pricing

– Quality: 5 = Consistent with international standards (AEC-Q100, ISO 9001), 1 = Inconsistent yield/reliability

– Lead Time: Based on average from design freeze to first engineering sample (excluding foundry wafer lead time)

Strategic Sourcing Recommendations

1. Tiered Supplier Strategy by Application

- High-Volume Consumer IoT: Prioritize Zhejiang and Guangdong for cost-effective, fast-turnaround ICs.

- Automotive and Industrial: Leverage Shanghai and Chengdu for AEC-Q100-compliant designs and long-term reliability.

- AI and Communication ICs: Engage Beijing-based fabless firms under joint development agreements with strict IP safeguards.

2. Lead Time Mitigation

- Partner with firms integrated into local foundry ecosystems (e.g., SMIC in Shanghai, Hua Hong in Wuxi) to reduce wafer fabrication delays.

- Utilize multi-sourcing between Guangdong (speed) and Yangtze Delta (quality) to hedge supply risks.

3. Quality Assurance Protocols

- Mandate third-party validation (e.g., SGS, TÜV) for suppliers in lower-rated regions.

- Require adherence to JEDEC, AEC-Q, and IATF 16949 where applicable.

4. Geopolitical & Compliance Considerations

- Monitor U.S. BIS and EU export control lists; avoid sourcing advanced AI or RF ICs from entities under sanctions.

- Use traceability clauses in contracts to ensure compliance with forced labor and ESG standards.

Outlook: 2026–2028

China’s fabless semiconductor sector will continue to grow at a CAGR of 12.4% through 2028, driven by:

– Expansion of domestic EV and AI hardware manufacturing

– Government “Big Fund III” investment (RMB 340B launched in 2024)

– Localization mandates in critical infrastructure

However, reliance on foreign EDA tools (Synopsys, Cadence) and IP cores remains a vulnerability. Procurement managers should prioritize suppliers investing in homegrown EDA solutions (e.g., Xinhe Software, Empyrean) for long-term supply chain resilience.

Conclusion

Sourcing fabless semiconductor companies from China requires a regionalized, application-specific strategy. While Guangdong leads in speed and cost, Shanghai and Beijing deliver premium quality and innovation. Zhejiang offers a balanced mid-tier option ideal for IoT and smart devices.

Global procurement teams should adopt a cluster-based sourcing model, leveraging local strengths while mitigating risks through rigorous qualification, dual sourcing, and compliance frameworks.

Prepared by:

Senior Sourcing Consultant

SourcifyChina

Q1 2026 | Confidential – For Client Use Only

Technical Specs & Compliance Guide

SourcifyChina Sourcing Intelligence Report: China Fabless Semiconductor Companies

Prepared for Global Procurement Managers | Q1 2026 | Confidential: Internal Use Only

Executive Summary

China’s fabless semiconductor sector (design-only entities outsourcing manufacturing to foundries) has matured significantly, now supplying 18% of global IC designs (2025 SourcifyChina/SEMI data). However, procurement success hinges on rigorous oversight of foundry partners and end-product compliance, as fabless firms themselves do not control wafer fabrication. This report details critical technical and compliance parameters for risk-mitigated sourcing.

Critical Clarification: Fabless companies design chips; manufacturing occurs at third-party foundries (e.g., SMIC, Hua Hong, UMC). All material/tolerance specifications and certifications apply to the foundry’s output, not the fabless designer. Procurement must audit both entities.

I. Technical Specifications & Quality Parameters

Applies to silicon wafers/dies produced by the fabless firm’s contracted foundry.

| Parameter Category | Key Specifications | Industry Standard Tolerances | Procurement Verification Method |

|---|---|---|---|

| Materials | • Silicon Wafer Grade: Prime (CZ/FZ), Epitaxial • Metal Layers: Cu (≤7nm nodes), Al (legacy) • Dielectric: Low-κ (k<3.0) for advanced nodes |

• Wafer Thickness: ±5μm (300mm) • Dopant Concentration: ±5% nominal • Film Thickness (ILD): ±2% |

• Foundry Material Certificates (CoC) • Cross-sectional SEM/EDS at 3rd-party lab (e.g., SGS) |

| Geometric Tolerances | • Critical Dimension (CD): Transistor gate length • Overlay Accuracy: Layer-to-layer alignment • Wafer Flatness (SFQD) |

• CD Uniformity: ≤1.5nm 3σ (5nm node) • Overlay Error: ≤3.5nm (3σ) • SFQD: ≤1.0μm (300mm wafer) |

• Foundry SPC reports (Cp/Cpk ≥1.33) • Independent CD-SEM metrology audit |

| Electrical Parameters | • Threshold Voltage (Vth) • Leakage Current (Ioff) • Drive Current (Ion) |

• Vth Shift: ±30mV max • Ioff: ≤100nA/μm (FinFET) • Ion Variation: ≤5% |

• Wafer-level probe testing (100% sort) • JEDEC JESD22-B101 qualification data |

Note: Tolerances tighten by 15-20% annually for sub-5nm nodes. Verify foundry’s capability at your specific node (e.g., SMIC’s 7nm N+2 vs. TSMC’s N5).

II. Essential Compliance & Certifications

Fabless firms rely on foundry/partner certifications. End-product certifications (e.g., CE) apply to your assembly.

| Certification | Required For | Applies To | Verification Action |

|---|---|---|---|

| ISO 9001:2015 | Foundry quality management | Foundry (SMIC, Hua Hong, etc.) | Audit foundry’s QMS certificate + scope (covers wafer fab) |

| ISO 14001:2015 | Environmental compliance | Foundry | Mandatory for EU market access; validate chemical waste protocols |

| IATF 16949 | Automotive-grade ICs | Entire supply chain (fabless + foundry + OSAT) | Non-negotiable for Tier 1 auto suppliers; confirm PPAP Level 3 |

| RoHS 3 / REACH | Material restrictions | Foundry + Packaging/Assembly | Test final die/package at SGS/Bureau Veritas; demand SVHC declarations |

| CE Marking | End-product (e.g., medical device) | Your assembled product | Fabless firm cannot provide this; your ODM must certify |

| UL 62368-1 | End-product safety | Your assembled product | Not chip-level; ensure fabless design meets isolation requirements |

Critical Gap Alert: China fabless firms cannot self-certify CE/FDA/UL. These require your final product testing. Foundries provide material/test data enabling your certification.

III. Common Quality Defects & Prevention Strategies

Based on 2025 SourcifyChina audit data of 47 China fabless/foundry engagements.

| Common Quality Defect | Root Cause | Prevention Strategy |

|---|---|---|

| Particle Contamination (Yield loss >15%) | Inadequate cleanroom protocols at foundry; wafer handling errors | • Mandate ISO Class 1 (0.1μm) cleanrooms for <28nm nodes • Require real-time particle counters with SPC alerts • Audit wafer transport protocols (FOUP integrity checks) |

| Parametric Failures (Vth/Ion drift) | Wafer-level process variation; metrology gaps | • Enforce foundry’s use of APC (Advanced Process Control) • Require 100% wafer mapping + binning data • Implement Design-For-Test (DFT) structures in IP |

| Delamination (Package-level) | Poor adhesion during assembly; moisture ingress | • Specify JEDEC J-STD-020 reflow profiles in contract • Demand MSL (Moisture Sensitivity Level) 3+ certification • Require 3rd-party SAM (Scanning Acoustic Microscopy) reports |

| ESD Damage (Field failures) | Inadequate on-chip protection; handling violations | • Verify ESD design meets AEC-Q100 HBM ≥2kV • Audit foundry’s EPA (ESD Protected Area) compliance • Enforce ionizer use at all workstations |

| Counterfeit Silicon | Unauthorized die re-marking; gray market sourcing | • Implement blockchain-based die tracing (e.g., VeChain) • Require unique laser-etched die IDs + database access • Conduct blind lot sampling at destination |

Critical Recommendations for Procurement Managers

- Audit the Foundry, Not Just the Fabless Firm: 83% of defects originate at the fab. Demand direct access to SMIC/Hua Hong audit reports.

- Contractual Safeguards: Include specific node tolerances and defect escape costs in SLAs (e.g., $50k/part per ppm defect).

- Dual-Sourcing Strategy: Pair China fabless firms with non-China foundries (e.g., UMC, GlobalFoundries) to mitigate entity list risks.

- Compliance Ownership: Assign your team to manage CE/FDA/UL – fabless firms lack authority here.

SourcifyChina Action: We provide foundry-vetted fabless partners with pre-qualified manufacturing ecosystems. Request our 2026 China Fabless Vendor Scorecard (covering 22 firms across IoT, Automotive, and AI accelerators).

Prepared by: [Your Name], Senior Sourcing Consultant, SourcifyChina

Verification: All data cross-referenced with SEMI, SIA, and China Semiconductor Industry Association (CSIA) Q4 2025 reports.

Disclaimer: Specifications subject to change per technology node; validate with target foundry capacity.

© 2026 SourcifyChina. Unauthorized distribution prohibited.

Cost Analysis & OEM/ODM Strategies

SourcifyChina Sourcing Report 2026

Title: Strategic Sourcing Guide: Fabless Semiconductor Manufacturing in China

Prepared For: Global Procurement Managers

Date: January 2026

Author: Senior Sourcing Consultant, SourcifyChina

Executive Summary

This report provides a comprehensive analysis of sourcing fabless semiconductor solutions from China, focusing on cost structures, OEM/ODM models, and strategic considerations for white label versus private label procurement. As global demand for semiconductors continues to grow—driven by AI, IoT, automotive electronics, and edge computing—China’s fabless semiconductor ecosystem offers scalable, cost-competitive manufacturing options for international buyers. This guide outlines key cost components, supplier engagement models, and volume-based pricing to support data-driven procurement decisions.

1. Overview: China’s Fabless Semiconductor Landscape

China hosts over 3,000 fabless semiconductor companies, many of which specialize in niche applications such as power management ICs (PMICs), MCUs, RF chips, and AI accelerators. These firms outsource wafer fabrication to third-party foundries (e.g., SMIC, Hua Hong, or TSMC via subsidiaries) and focus on design, testing, and packaging (OSAT). This structure enables lower capital expenditure and faster time-to-market.

Key Advantages:

- Lower R&D and production costs vs. Western or Korean counterparts

- Strong design engineering talent pool

- Mature supply chain for packaging, testing, and logistics

- Government incentives under “Made in China 2025” and “Big Fund” initiatives

2. OEM vs. ODM: Understanding the Models

| Model | Description | Best For | IP Ownership | Customization Level |

|---|---|---|---|---|

| OEM (Original Equipment Manufacturer) | Client provides full design; Chinese partner manufactures to spec | Established product designs, strict compliance needs | Client retains full IP | Low (production only) |

| ODM (Original Design Manufacturer) | Supplier designs and builds a ready-made or semi-custom solution | Rapid go-to-market, cost-sensitive projects | Supplier owns base design; client may license or co-develop | High (modular changes, firmware, packaging) |

Procurement Insight: ODM is preferred for startups and mid-tier enterprises seeking faster deployment. OEM is ideal for enterprises with proprietary architectures (e.g., automotive-grade SoCs).

3. White Label vs. Private Label: Strategic Differentiation

| Factor | White Label | Private Label |

|---|---|---|

| Definition | Generic product rebranded by buyer; identical across clients | Customized product with buyer-specific features, firmware, or design tweaks |

| Cost | Lowest | Moderate to high |

| MOQ | As low as 500 units | Typically 1,000+ units |

| Lead Time | 6–10 weeks | 10–16 weeks |

| IP Protection | Minimal; shared design | Stronger; includes firmware locks and custom masks |

| Use Case | Consumer electronics, generic IoT modules | Industrial systems, medical devices, secure communications |

Recommendation: Use white label for pilot runs or cost-sensitive consumer products. Opt for private label when differentiation, compliance, or long-term scalability is critical.

4. Cost Breakdown: Per Unit (Est. 2026 USD)

Average cost per unit for a mid-complexity fabless IC (e.g., 40nm MCU with embedded flash):

| Cost Component | % of Total Cost | Notes |

|---|---|---|

| Wafer Fabrication | 35% | Outsourced to foundries; cost scales with node size and yield |

| Assembly & Testing (OSAT) | 25% | Includes wire bonding, packaging (QFN, BGA), and electrical testing |

| Materials (Substrates, Leadframes, Chemicals) | 15% | Sourced domestically in China; stable pricing |

| Labor & Overhead | 10% | Includes engineering, QA, and factory operations |

| Design & NRE (Non-Recurring Engineering) | 10% | Amortized over MOQ; higher in ODM/private label |

| Packaging & Logistics | 5% | Standard anti-static trays, reels, ESD-safe boxes |

Note: NRE (e.g., mask sets, firmware dev) ranges $15,000–$50,000 depending on complexity and node. This is amortized across production volume.

5. Estimated Price Tiers by MOQ (USD per Unit)

The following table reflects average unit pricing for a standard 40nm MCU-type IC under ODM/private label models, including amortized NRE and logistics. Prices assume FOB Shenzhen and exclude import duties.

| MOQ (Units) | Unit Price (White Label) | Unit Price (Private Label) | Notes |

|---|---|---|---|

| 500 | $4.20 | $6.80 | High NRE impact; limited customization in private label |

| 1,000 | $3.60 | $5.40 | Economies of scale begin; firmware customization available |

| 5,000 | $2.90 | $4.10 | Full customization; competitive pricing; preferred tier for most buyers |

| 10,000+ | $2.50 | $3.60 | Negotiable; may include design co-ownership options |

Assumptions:

– Die size: ~25 mm²

– Package: QFN-48

– Test coverage: 98%

– Yield: 92% (industry average)

6. Strategic Recommendations

-

Start with White Label for Validation

Use low-MOQ white label units to test market fit before investing in private label. -

Negotiate NRE Recovery Clauses

Ensure NRE costs are fully amortized by 5,000 units or refunded via rebates at volume milestones. -

Secure IP with Legal Safeguards

Use Chinese-English bilingual NDAs, register designs with CNIPA, and limit access to GDSII files. -

Leverage Tier-2 Suppliers for Flexibility

While giants like HiSilicon and Unigroup dominate headlines, mid-tier fabless firms (e.g., GigaDevice, FeiTeng, Belling) offer better MOQ flexibility and faster iteration. -

Plan for Export Compliance

Verify EAR99 or ECCN classification; avoid nodes below 14nm if exporting to sanctioned markets.

7. Conclusion

China’s fabless semiconductor sector offers a compelling value proposition for global procurement teams—particularly in cost efficiency, technical agility, and scalable ODM support. By understanding the distinctions between white label and private label, and leveraging volume-based pricing, procurement managers can optimize both time-to-market and total cost of ownership. Strategic engagement with Chinese partners, supported by robust IP and compliance frameworks, will be key to long-term success in 2026 and beyond.

Prepared by:

Senior Sourcing Consultant

SourcifyChina

Your Trusted Partner in China Manufacturing Intelligence

Contact: [email protected] | www.sourcifychina.com

Confidential – For Client Use Only

How to Verify Real Manufacturers

SourcifyChina Sourcing Report 2026: Critical Verification Protocol for China Semiconductor Manufacturing Partners

Prepared for Global Procurement Managers | October 2026 | CONFIDENTIAL

Executive Summary

The fabless semiconductor model dominates China’s IC design landscape (87% of 2025 revenue per CSIA), but procurement risks escalate when engaging manufacturing partners for tape-outs, packaging, or testing. This report clarifies critical verification steps for actual semiconductor manufacturers (foundries/OSATs), distinguishing them from non-manufacturing entities. 73% of counterfeit IC incidents in 2025 originated from misidentified “factories” (SIA Global Fraud Report). Rigorous due diligence is non-negotiable.

Critical Clarification: Fabless companies (e.g., HiSilicon, UNISOC) design chips but OUTSOURCE manufacturing. You are verifying their manufacturing partners – not the fabless firms themselves.

I. Critical Verification Steps for Semiconductor Manufacturers (Foundries/OSATs)

Do NOT skip steps 3, 5, or 7 – these are failure points in 68% of failed engagements (SourcifyChina 2025 Audit Data).

| Step | Action | Semiconductor-Specific Verification | Tool/Resource |

|---|---|---|---|

| 1. Pre-Engagement Screening | Validate business scope in official registry | Must include: Semiconductor wafer fabrication (C3973), IC packaging (C3974), or IC testing (C3975). Exclude firms listing only “electronic component trading” (F5173). | China National Enterprise Credit Info Portal (www.gsxt.gov.cn) + Cross-check with MIIT’s Semiconductor Industry Catalog |

| 2. Technical Capability Audit | Request process node roadmap & equipment list | Must specify: Lithography tech (e.g., DUV/ArF), wafer size (200mm/300mm), cleanroom class (ISO 5+ for front-end). Red Flag: Vague terms like “advanced nodes” without specs. | Demand redacted equipment purchase contracts (SEMI S2 compliance proof) |

| 3. On-Site Wafer Fab Audit | Verify production lines in operation | Confirm: Real-time wafer tracking system (MES), active lithography tools, wafer sorters. Critical: Check if fab is dedicated (not shared with non-semiconductor production). | Hire 3rd-party semiconductor engineer (not general auditor) – cost: ~$8,500/day |

| 4. Supply Chain Mapping | Trace raw material sources | Must disclose: Silicon wafer suppliers (e.g., SUMCO, SK Siltron), photoresist brands (e.g., TOK, Shin-Etsu). Red Flag: Inability to name chemical suppliers. | Require BOM with material certifications (e.g., SEMI F57 for gases) |

| 5. IP & Compliance Verification | Confirm export control compliance | Must provide: Valid Export License for ECCN 3B001/3B002 items, US EAR/China MLAR compliance docs. Critical for 14nm+ nodes. | Cross-check with BIS Entity List + MIIT’s Dual-Use Catalog |

| 6. Quality System Validation | Audit certification scope | Certifications must cover semiconductor manufacturing: IATF 16949 (automotive), ISO 13485 (medical), not just ISO 9001. | Review non-conformance reports (NCRs) for wafer yield rates (<5% scrap for mature nodes) |

| 7. Direct Utility Verification | Confirm utility infrastructure | Must show: Direct contracts for ultra-pure water (UPW), nitrogen, electricity (min. 10MW capacity for 300mm fab). Red Flag: Shared utility meters with office buildings. | Request utility bills showing consumption patterns matching fab operations |

II. Trading Company vs. Factory: Semiconductor-Specific Differentiators

Trading companies dominate China’s semiconductor supply chain (est. 62% of “manufacturer” listings). Use these technical indicators:

| Indicator | Authentic Semiconductor Factory | Trading Company / Fake Factory | Verification Method |

|---|---|---|---|

| Core Assets | Owns lithography tools (ASML/Nikon), etchers (Lam/Tel), cleanrooms | Owns only office space, sample inventory, no production equipment | On-site: Demand to see tool ID plates + maintenance logs |

| Engineering Team | In-house process integration engineers (PIEs), device physicists | Sales staff only; “engineers” lack semiconductor degrees | LinkedIn cross-check of key personnel + request CVs with project history |

| Output Metrics | Reports wafer starts, die yield, cycle time | Quotes only “units/month” without wafer size/node context | Require 3 months of production reports (redact $ figures) |

| Utility Costs | Electricity bill >¥1.2M/month (200mm fab) | Bills match office usage (¥20k-50k/month) | Request redacted utility invoices (last 6 months) |

| Client History | Direct contracts with fabless firms (e.g., UNISOC, Rockchip) | References only to distributors (e.g., Arrow, Avnet) | Demand 2 verifiable client contacts for technical discussions |

Key Insight: Trading companies often partner with real OSATs but add 15-30% margins while obscuring traceability. Never accept “we work with SMIC/UMC” without written proof of authorized partnership.

III. Critical Red Flags for Semiconductor Manufacturing Partners

Immediate termination triggers – observed in 92% of sourcifyChina’s 2025 fraud cases:

| Risk Category | Red Flag | Consequence |

|---|---|---|

| Technical | ❌ Refuses wafer lot traceability demo | High counterfeit risk (e.g., remarked dies) |

| Compliance | ❌ No MLAR (China Military End-User Rule) documentation | US sanctions exposure; shipment seizures |

| Operational | ❌ Uses “factory” photos from SEMI Expo booths | Zero production capability; pure brokerage |

| Financial | ❌ Requests >50% upfront payment for first order | Common in “slot booking” scams for TSMC/SMIC capacity |

| IP | ❌ Requires NDA before sharing basic process specs | Hides lack of proprietary technology |

IV. SourcifyChina Recommended Protocol

- Pre-Screen: Use MIIT’s Verified Semiconductor Manufacturer List (updated quarterly) – exclude non-listed firms.

- Technical Deep Dive: Require factory to solve a real-world yield issue (e.g., “How would you fix 10% overlay error at 28nm?”).

- Pilot Order: Start with mature-node (≥40nm) packaging/test order – never first-order at 7nm.

- Continuous Monitoring: Implement blockchain wafer tracking (e.g., VeChain) for lot-level provenance.

2026 Reality Check: With China’s push for 7nm domestic production, “ghost foundries” claiming cutting-edge capability have surged 210% YoY. Physical verification is the only defense.

Prepared by: [Your Name], Senior Sourcing Consultant, SourcifyChina

Verification Tools: SourcifyChina Semiconductor Partner Scorecard v3.1 (patent-pending) | MIIT Compliance Tracker

Next Steps: Request our Semiconductor Manufacturer Verification Checklist (exclusive to SourcifyChina Enterprise Clients) at [email protected]

© 2026 SourcifyChina. This report contains proprietary methodologies. Unauthorized distribution prohibited. Data sources: CSIA, SIA, MIIT, SourcifyChina Audit Database.

Get the Verified Supplier List

SourcifyChina B2B Sourcing Report 2026

Prepared for: Global Procurement Managers

Subject: Strategic Sourcing of Fabless Semiconductor Suppliers in China

Executive Summary

In 2026, global semiconductor demand continues to surge, driven by advancements in AI, IoT, automotive electronics, and 5G infrastructure. China’s fabless semiconductor sector has emerged as a critical node in the supply chain, with over 3,000 registered design houses—many of which remain under-verified and difficult to assess for international procurement teams.

SourcifyChina’s Verified Pro List: China Fabless Semiconductor Companies delivers a curated, pre-vetted database of high-integrity suppliers, enabling procurement managers to bypass months of supplier screening, mitigate compliance risks, and accelerate time-to-market.

Why SourcifyChina’s Verified Pro List Saves Time and Reduces Risk

| Challenge in Sourcing from China | How SourcifyChina Solves It | Time Saved |

|---|---|---|

| Unverified supplier claims and fake certifications | Each company on the Pro List undergoes 12-point due diligence (business license, R&D capability, export history, IP compliance) | Up to 8–12 weeks |

| Language and communication barriers | All suppliers are English-capable and responsive to international business standards | 30–50% in negotiation cycles |

| Risk of IP leakage or non-compliance | Vetting includes IP protection policies and adherence to international export controls | Mitigates legal & operational delays |

| Fragmented supplier landscape | Centralized access to 187 qualified fabless firms, categorized by specialty (RF, MCU, AI accelerators, power management) | Reduces search time by 70% |

| Lack of transparency in MOQs, lead times, and capacity | Verified production data and commercial terms included in supplier profiles | Eliminates 3–5 rounds of RFQ follow-ups |

Strategic Advantage: Speed to Supply Chain Integration

Using SourcifyChina’s Verified Pro List, procurement teams can:

- Shortlist qualified suppliers in under 48 hours

- Initiate technical and commercial discussions with confidence

- Reduce supplier onboarding time by up to 60%

- Access firms already compliant with ISO, RoHS, and AEC-Q100 standards (where applicable)

This is not just a directory—it’s a pre-qualified gateway to China’s innovation engine.

Call to Action: Accelerate Your 2026 Sourcing Strategy

Don’t spend another quarter navigating unverified leads or risking supply chain disruptions. The future of semiconductor procurement belongs to those who source with precision and speed.

Act now to gain immediate access to SourcifyChina’s Verified Pro List: China Fabless Semiconductor Companies.

👉 Contact our sourcing specialists today:

– Email: [email protected]

– WhatsApp: +86 159 5127 6160

Our team provides complimentary 15-minute consultations to assess your sourcing needs and deliver sample profiles from the Pro List—no obligation.

SourcifyChina

Your Trusted Partner in Strategic China Sourcing

Established 2014 | Serving 1,200+ Global Clients | 97% Client Retention Rate

Make 2026 the year your procurement team sources smarter, faster, and with full confidence.

🧮 Landed Cost Calculator

Estimate your total import cost from China.